# DATA IMAGE CORPORATION

# TFT Module Specification PRELIMINARY

ITEM NO.: FG030562DSSWBG02

# **Table of Contents**

| 1.  | COVER & CONTENTS ·····            | 1  |

|-----|-----------------------------------|----|

| 2.  | RECORD OF REVISION ······         | 2  |

| 3.  | FEATURES                          | 3  |

| 4.  | GENERAL SPECIFICATIONS            | 3  |

| 5.  | ABSOLUTE MAXIMUM RATINGS          | 3  |

| 6.  | ELECTRICAL CHARACTERISTICS ······ | 4  |

| 7.  | BLOCK DIAGRAM ······              | 5  |

| 8.  | INPUT / OUTPUT TERMINALS          | 6  |

| 9.  | AC CHARACTERISTICS ······         | 8  |

| 10. | COMMAND DESCRIPTION ······        | 20 |

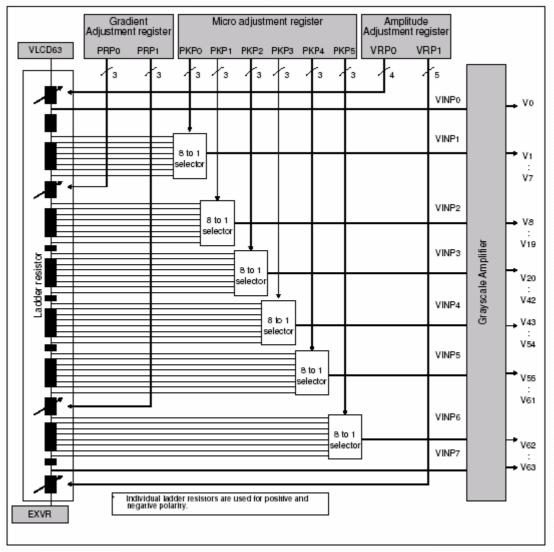

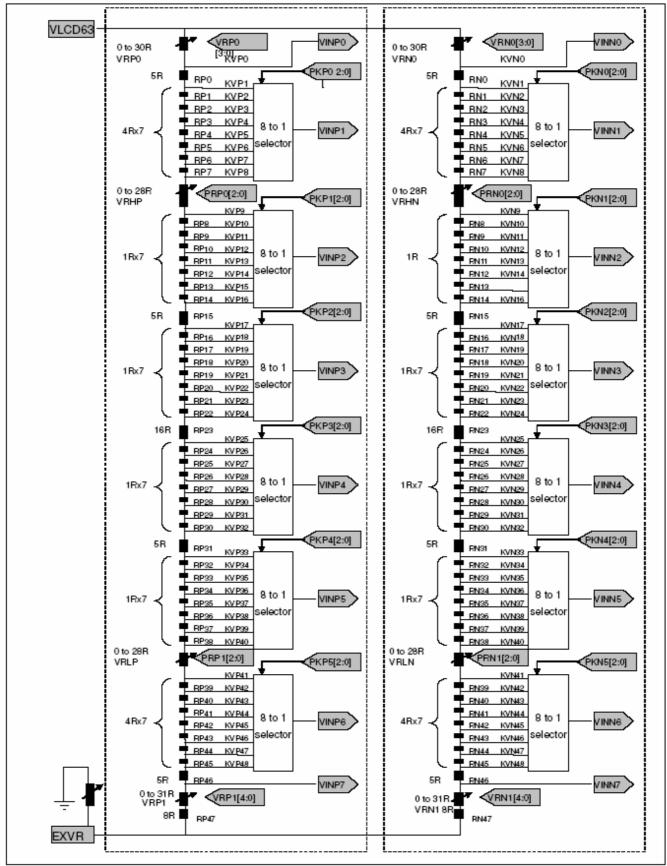

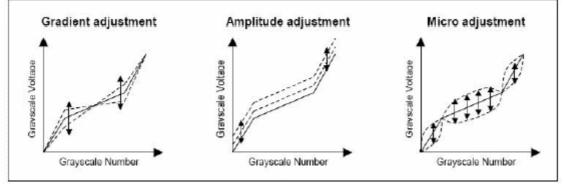

| 11. | GAMMA ADJUSTMENT FUNCTION         | 36 |

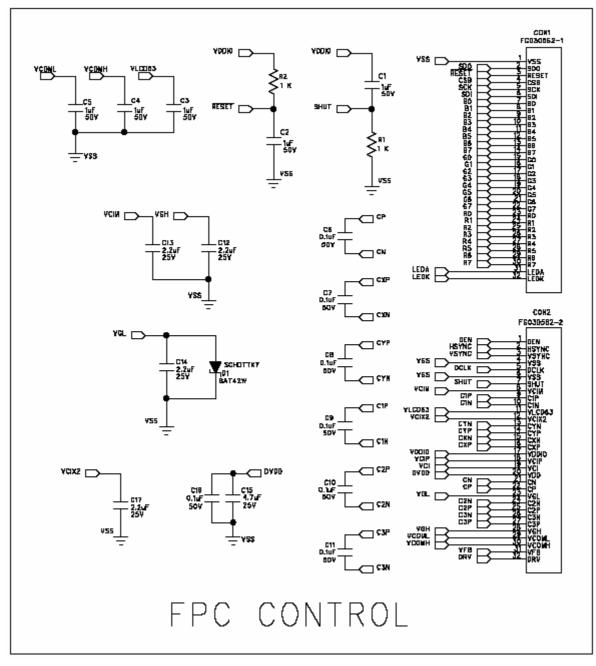

| 12. | APPLIICATION CIRCUIT ······       | 41 |

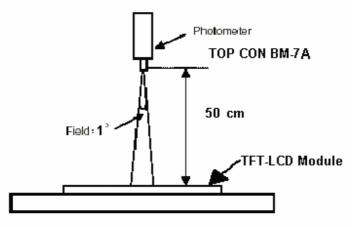

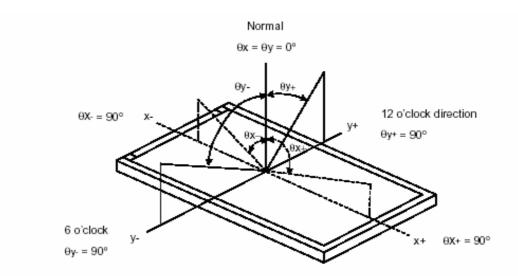

| 13. | OPTICAL CHARACTERISTIC ······     | 43 |

| 14. | QUALITY ASSURANCE ·····           | 46 |

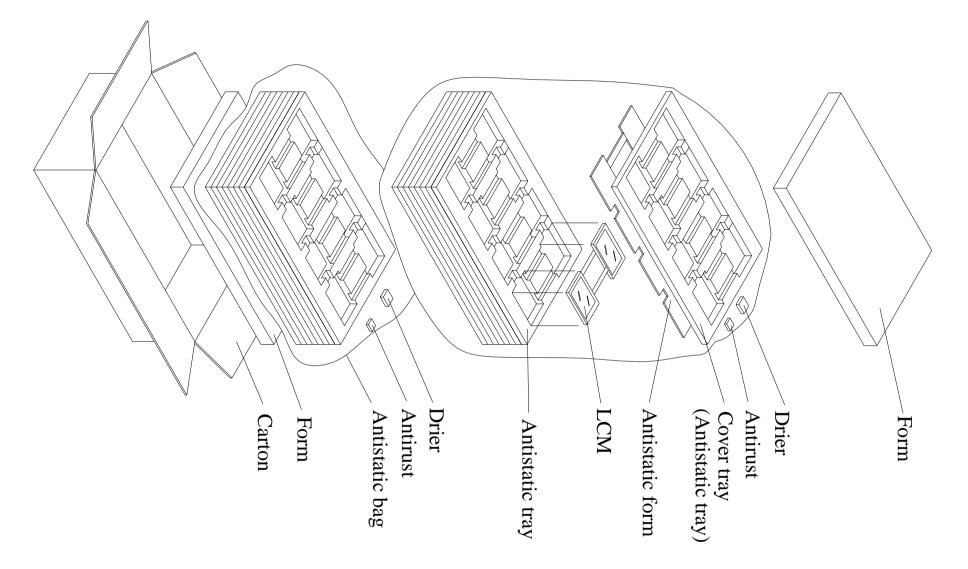

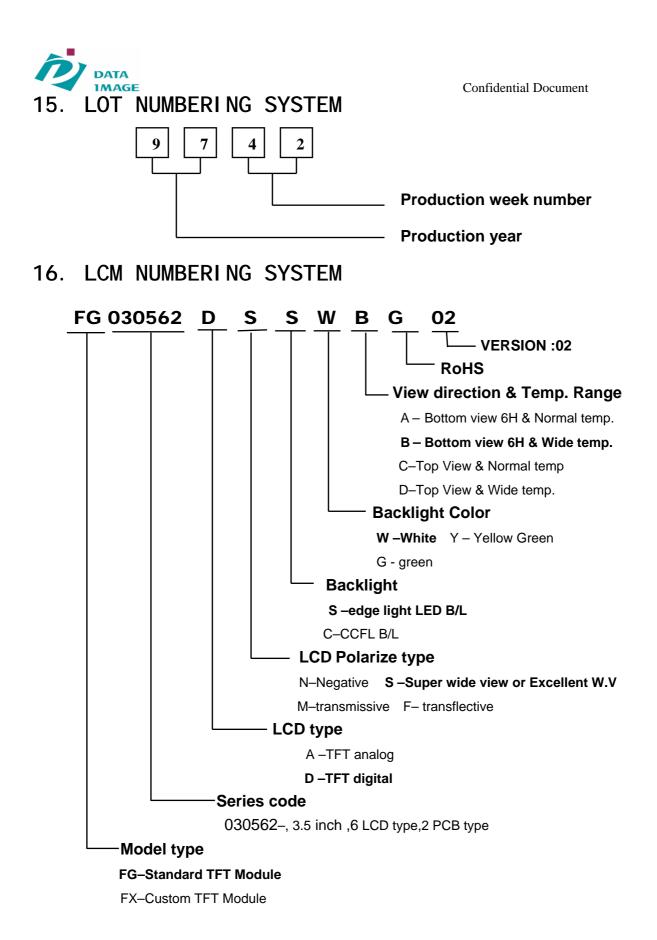

| 15. | LOT NUMBERING SYSTEM ·····        | 47 |

| 16. | LCM NUMBERING SYSTEM ·····        | 47 |

| 17. | PRECAUTIONS IN USE LCM            | 48 |

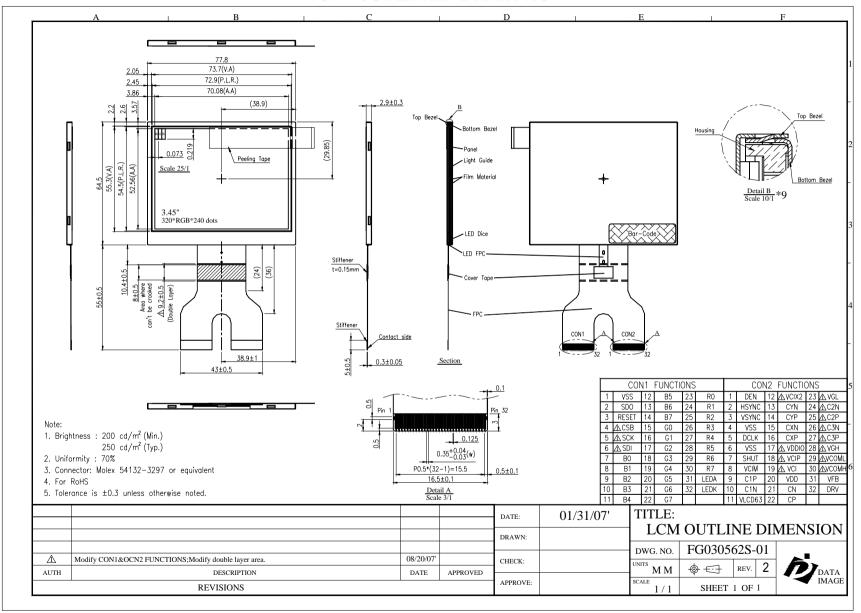

| 18. | OUTLINE DRAWING ·····             | 49 |

| 19. | PACKAGE INFORMATION ·····         | 50 |

| Customer Companies | R&D Dept. | Q.C. Dept.   | Eng. Dept.  | Prod. Dept.  |

|--------------------|-----------|--------------|-------------|--------------|

|                    | ALEX      | ERIC         | GARY        | HUANG        |

| Approved by        | Version:  | Issued Date: | Sheet Code: | Total Pages: |

|                    | 1         | 2007/10/29   |             | 50           |

| Rev | Date      | Item | Page | Comment             |

|-----|-----------|------|------|---------------------|

| 1   | 29/OCT/07 |      |      | Initial PRELIMINARY |

|     |           |      |      |                     |

|     |           |      |      |                     |

|     |           |      |      |                     |

|     |           |      |      |                     |

|     |           |      |      |                     |

|     |           |      |      |                     |

|     |           |      |      |                     |

|     |           |      |      |                     |

|     |           |      |      |                     |

|     |           |      |      |                     |

|     |           |      |      |                     |

|     |           |      |      |                     |

|     |           |      |      |                     |

|     |           |      |      |                     |

|     |           |      |      |                     |

|     |           |      |      |                     |

|     |           |      |      |                     |

|     |           |      |      |                     |

|     |           |      |      |                     |

|     |           |      |      |                     |

|     |           |      |      |                     |

- Support CCIR656/CCIR601 8 bit format or 8 bit serial RGB or 24 bit parallel RGB.

- Support the SPI commands setting, the operation parameters setting internally.

- Our components and processes are compliant to RoHS standard

- Support Contrast/Brightness control.

- On-chip voltage generator.

- On-chip DC-DC converter up to 6x / -6x.

- Programmable gamma correction curve.

- Non-Volatile Memory (OTP) for VCOM calibration

# 4. GENERAL SPECIFICATIONS

| Parameter            |           | Specifications               | Unit |

|----------------------|-----------|------------------------------|------|

| Screen Size          |           | 3.45" (diagonal)             | inch |

| Surface Treatment    |           | Anti-Glare                   |      |

| Display Format       |           | 320 X RGB X 240              | dots |

| Active Area          |           | 70.08 (W) x 52.56 (H)        | mm   |

| Dot Pitch            |           | 0.073(W) x 0.219 (H)         | mm   |

| Pixel Configuration  |           | Stripe                       |      |

| Outline Dimension    |           | 77.8 (W) x 64.5 (H) x 2.9(T) | mm   |

| Weight               |           | 34                           | g    |

| View Angle direction |           | 6 o'clock                    |      |

| Temperature Range    | Operation | -20~70                       | °C   |

| remperature Mange    | Storage   | -30~80                       | °C   |

# 5. ABSOLUTE MAXIMUM RATINGS

|                          |        |      | (VS  | SS=0∨) |

|--------------------------|--------|------|------|--------|

| Parameter                | Symbol | MIN. | MAX. | Unit   |

| Power supply voltage (1) | VDDIO  | -0.3 | +4.0 | V      |

| Power supply voltage (2) | VDD    | -0.3 | +2.7 | V      |

| Input voltage            | VCI    | -0.3 | +5.0 | V      |

Note:

\*All of the voltages listed above are with respective to VSS= 0V.

\*Device is subject to be damaged permanently if stresses beyond those absolute maximum ratings listed above.

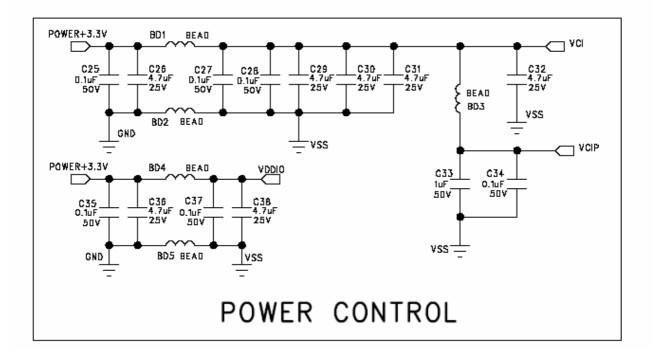

# **6. ELECTRICAL CHARACTERISTICS**

6.1 DC Electrical Characteristics

(Unless otherwise specified, Voltage Referenced to  $V_{SS=0V}$ ,  $V_{DDIO} = 3.3V$ , Ta = 25)

| Symbol | Parameter                              | Test condition                                            | Min       | Тур   | Max       | Unit |

|--------|----------------------------------------|-----------------------------------------------------------|-----------|-------|-----------|------|

| Vddio  | Power supply pin of the logic block    | Recommend Operating Voltage<br>Possible Operating Voltage | 2.5       | 3.3   | 3.6       | V    |

| Vcı    | Booster Reference Supply Voltage Range | Recommend Operating Voltage<br>Possible Operating Voltage | VDDIO     | 3.3   | 3.6       | V    |

| VCIP   | Voltage supply pin for analog circuit  |                                                           | Vcı       | Vcı   | Vcı       | V    |

| Vсомн  | VCOM High Output Voltage               |                                                           | 3.4       | 3.7   | 4.0       | V    |

| VCOML  | VCOM Low Output Voltage                |                                                           | -1.88     | -1.58 | -1.28     | V    |

| VOOM   | VCOM-AC                                |                                                           | -         | 5.6   | -         | VP-P |

| VCOM   | VCOM-DC                                |                                                           | -         | 1.12  | -         | V    |

| Voh1   | Logic High Output Voltage              | l out = -100µA                                            | 0.9*Vddio | -     | Vddio     | V    |

| Vol1   | Logic Low Output Voltage               | l out = 100µA                                             | 0         | -     | 0.1*Vddio | V    |

| VIH1   | Logic High Input voltage               |                                                           | 0.8*Vddio | -     | Vddio     | V    |

| VIL1   | Logic Low Input voltage                |                                                           | 0         | -     | 0.2*VDDIO | V    |

| VGH    | Gate driver High Output Voltage        |                                                           | -         | +15   | -         | V    |

| VGL    | Gate driver Low Output Voltage         |                                                           | -         | -10   | -         | V    |

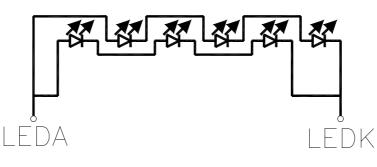

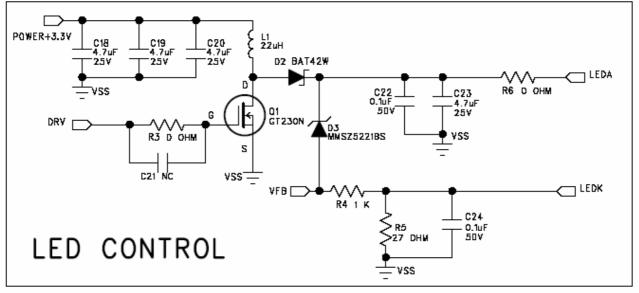

# 6.2 LED Back-light Driving Section

| Parameter   | Symbol | Min. | Тур. | Max. | Unit | Remark                |

|-------------|--------|------|------|------|------|-----------------------|

| LED voltage | VL     | 9.6  | 10.2 | 11.4 | V    | $I_L=40$ mA Ta= 25 °C |

| LED current | ΙL     |      | 40   |      | mA   | Ta= 25 °C             |

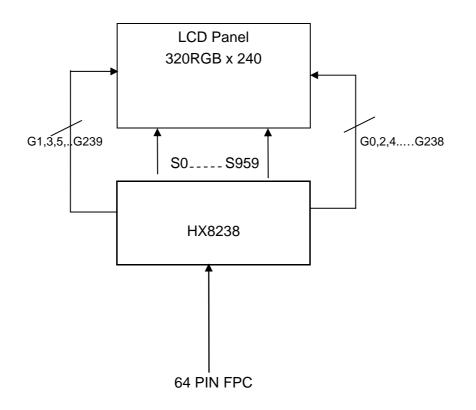

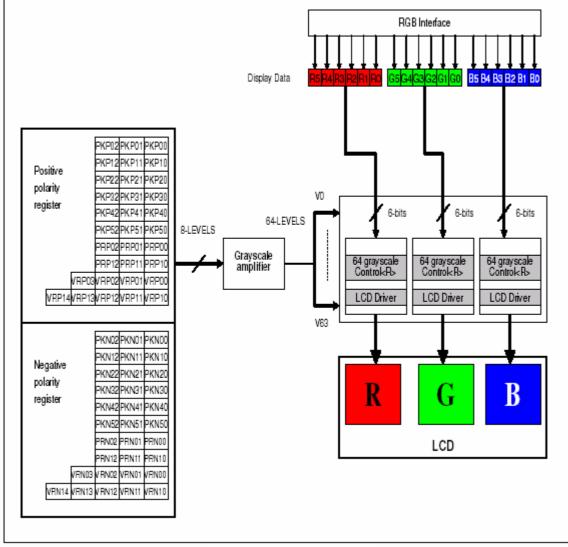

# 7. BLOCK DIAGRAM

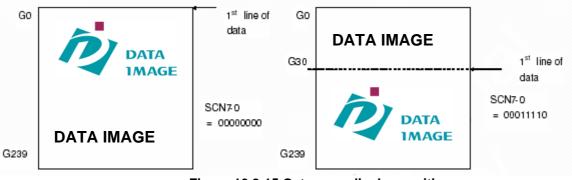

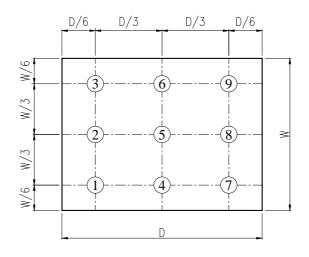

# Correspondence between Data and Display Position

|       | S0000 \$ | S0001 | S0002 | S0003 | S0004 | S0005 | S0006 | S0007 |   | S958 | S959 |

|-------|----------|-------|-------|-------|-------|-------|-------|-------|---|------|------|

| G000  | R001     | G001  | B001  | R002  | G002  | B002  | R003  | G003  |   | G320 | B320 |

|       | T        |       |       |       |       |       |       |       |   |      |      |

|       |          |       |       |       |       |       |       |       |   |      |      |

| i     | 1        |       |       |       |       | I     |       | I     | I |      |      |

| G2'39 | R001     | G001  | B001  | R002  | G002  | B002  | R003  | G003  |   | G320 | B320 |

# 8. 1 PIN Connections CON1

| Pin No | Symbol | I/O | Description                                                                             |  |  |  |  |

|--------|--------|-----|-----------------------------------------------------------------------------------------|--|--|--|--|

| 1      | VSS    | VI  | Ground                                                                                  |  |  |  |  |

| 2      | SDO    | 0   | Data Output pin in Serial mode. leave it OPEN when not used.                            |  |  |  |  |

| 3      | RESET  | Ι   | Hardware global reset. Low active. Normally pull high.                                  |  |  |  |  |

| 4      | CSB    | Ι   | Serial port Data Enable Signal. Internal pull high, leave it OPEN when not used.        |  |  |  |  |

| 5      | SCK    | Ι   | Serial port Clock. Internal pull high, leave it OPEN when not used.                     |  |  |  |  |

| 6      | SDI    | Ι   | Serial port Data input. Internal pull high, leave it OPEN when not used.                |  |  |  |  |

| 7      | B0     | Ι   |                                                                                         |  |  |  |  |

| 8      | B1     | Ι   |                                                                                         |  |  |  |  |

| 9      | B2     | Ι   | Digital data input. B0 is LSB and B7 is MSB                                             |  |  |  |  |

| 10     | B3     | Ι   | 1.If parallel RGB input mode is used, BX, GX, and RX indicate B, G, and R data in turn. |  |  |  |  |

| 11     | B4     | Ι   | 2.If serial RGB or CCIR601/656 input mode is select, only R0 – R7 are used,             |  |  |  |  |

| 12     | B5     | Ι   | and others (BX, GX) short to VSS or floating.                                           |  |  |  |  |

| 13     | B6     | Ι   |                                                                                         |  |  |  |  |

| 14     | B7     | Ι   |                                                                                         |  |  |  |  |

| 15     | G0     | Ι   |                                                                                         |  |  |  |  |

| 16     | G1     | Ι   |                                                                                         |  |  |  |  |

| 17     | G2     | Ι   | Digital data input. G0 is LSB and G7 is MSB                                             |  |  |  |  |

| 18     | G3     | Ι   | 1.If parallel RGB input mode is used, BX, GX, and RX indicate B, G, and R data          |  |  |  |  |

| 19     | G4     | Ι   | in turn.<br>2.If serial RGB or CCIR601/656 input mode is select, only R0 – R7 are used, |  |  |  |  |

| 20     | G5     | Ι   | and others (BX, GX) short to VSS or floating.                                           |  |  |  |  |

| 21     | G6     | Ι   |                                                                                         |  |  |  |  |

| 22     | G7     | Ι   |                                                                                         |  |  |  |  |

| 23     | R0     | Ι   |                                                                                         |  |  |  |  |

| 24     | R1     | Ι   |                                                                                         |  |  |  |  |

| 25     | R2     | Ι   | Digital data input. R0 is LSB and R7 is MSB                                             |  |  |  |  |

| 26     | R3     | Ι   | 1.If parallel RGB input mode is used, BX, GX, and RX indicate B, G, and R data in turn. |  |  |  |  |

| 27     | R4     | Ι   | 2.If serial RGB or CCIR601/656 input mode is select, only R0 - R7 are used,             |  |  |  |  |

| 28     | R5     | Ι   | and others (BX, GX) short to VSS or floating.                                           |  |  |  |  |

| 29     | R6     | Ι   |                                                                                         |  |  |  |  |

| 30     | R7     | Η   |                                                                                         |  |  |  |  |

| 31     | LEDA   | VI  | Power supply of back light.                                                             |  |  |  |  |

| 32     | LEDK   | VI  | Ground of back light.                                                                   |  |  |  |  |

# 8. 2 PIN Connections CON2

| Pin No | Symbol | I/O | Description                                                                                |

|--------|--------|-----|--------------------------------------------------------------------------------------------|

| 1      | DEN    | Ι   | Data Enable pin, connect to VDDIO or floating if not used.                                 |

| 2      | HSYNC  | Ι   | Line synchronization signal, connect to VDDIO or floating if not used.                     |

| 3      | VSYNC  | Ι   | Frame synchronization signal, connect to VDDIO or floating if not used.                    |

| 4      | VSS    | VI  | Ground                                                                                     |

| 5      | DCLK   | I   | Dot-Clock signal.                                                                          |

| 6      | VSS    | VI  | Ground                                                                                     |

| 7      | SHUT   | Ι   | Disobey shut down pin to put the driver into sleep mode. Internal pull low.                |

| 8      | VCIM   | 0   | Negative voltage of VCI. Please connect a capacitor for stabilization.                     |

| 9      | C1P    | Ι   | Connect a capacitor to C1N.                                                                |

| 10     | C1N    | Ι   | Connect a capacitor to C1P.                                                                |

| 11     | VLCD63 | 0   | Internal generated power for source driver. Please connect a capacitor for stabilization.  |

| 12     | VCIX2  | Ι   | Equals to 2xVCI. Please connect a capacitor for stabilization.                             |

| 13     | CYN    | Ι   | Connect a capacitor to CYP.                                                                |

| 14     | CYP    | Ι   | Connect a capacitor to CYN.                                                                |

| 15     | CXN    | Ι   | Connect a capacitor to CXP.                                                                |

| 16     | CXP    | Ι   | Connect a capacitor to CXN.                                                                |

| 17     | VDDIO  | VI  | Voltage input pin for I/O logic.                                                           |

| 18     | VCIP   | VI  | Voltage supply pin for analog circuit. Connect to same source of VCI.                      |

| 19     | VCI    | VI  | Booster input voltage pin. 2.5V~3.6V                                                       |

| 20     | VDD    | VO  | VDD is connecting with internal regulator. Please connect a capacitor for stabilization.   |

| 21     | CN     | Ι   | Connect a capacitor to CP.                                                                 |

| 22     | СР     | Ι   | Connect a capacitor to CN.                                                                 |

| 23     | VGL    | 0   | A negative power output pin for gate driver. Please connect a capacitor for stabilization. |

| 24     | C2N    | Ι   | Connect a capacitor to C2P.                                                                |

| 25     | C2P    | Ι   | Connect a capacitor to C2N.                                                                |

| 26     | C3N    | Ι   | Connect a capacitor to C3P.                                                                |

| 27     | C3P    | Ι   | Connect a capacitor to C3N.                                                                |

| 28     | VGH    | 0   | A positive power output pin for gate driver. Please connect a capacitor for stabilization. |

| 29     | VCOML  | 0   | This pin indicates a LOW level of VCOM generated in driving the VCOM alternation.          |

| 30     | VCOMH  | 0   | This pin indicates a HIGH level of VCOM generated in driving the VCOM alternation.         |

| 31     | VFB    | Ι   | Main boost regulator feedback input. Connect feedback resistive divider to VSS.            |

| 32     | DRV    | 0   | Power transistor gate single for the boost converter.                                      |

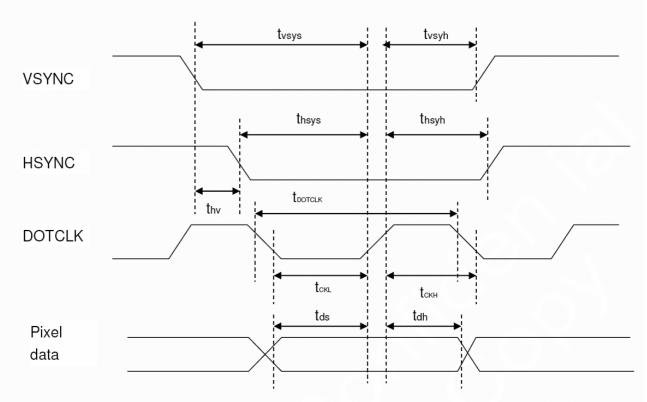

# 9.1 AC Characteristics

(Unless otherwise specified, Voltage Referenced to  $V_{SS}=0V$ ,  $V_{DDIO} = 3.3V$ , Ta = 25)

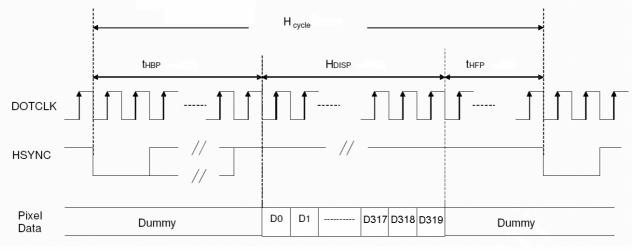

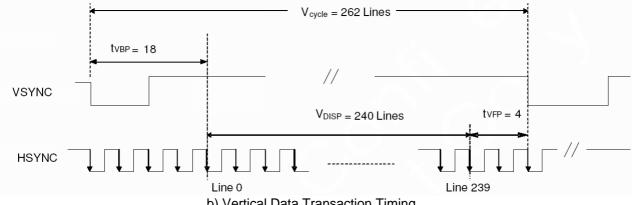

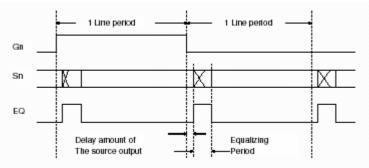

# Figure 9.1-1 Pixel timing

| Characteristics                                 | Symbol  | М           | in    | Ту     | Тур   |        | ax    | Unit    |

|-------------------------------------------------|---------|-------------|-------|--------|-------|--------|-------|---------|

| Characteristics                                 | Symbol  | 24 bit      | 8 bit | 24 bit | 8 bit | 24 bit | 8 bit | Unit    |

| DOTCLK Frequency                                | fDOTCLK |             |       | 6.5    | 19.5  | 10     | 30    | MHz     |

| DOTCLK Period                                   | tDOTCLK | 100         | 33.3  | 154    | 51.3  | -      | -     | ns      |

| Vertical Sync Setup Time                        | tvsys   | 20          | 10    | -      | -     | -      | -     | ns      |

| Vertical Sync Hold Time                         | tvsyh   | tvsyh 20 10 |       |        | -     | -      | -     | ns      |

| Horizontal Sync Setup Time                      | thsys   | 20          | 10    | -      | -     | -      | -     | ns      |

| Horizontal Sync Hold Time                       | thsyh   | 20          | 10    | -      | -     | -      | -     | ns      |

| Phase difference of Sync<br>Signal Falling Edge | thv     | 1           |       | -      |       | 240    |       | tDOTCLK |

| DOTCLK Low Period                               | tCKL    | 50          | 15    | -      | -     | -      | -     | ns      |

| DOTCLK High Period                              | tCKH    | 50          | 15    | -      | -     | -      | -     | ns      |

| Data Setup Time                                 | tds     | 12 10       |       | -      | -     | -      | -     | ns      |

| Data hold Time                                  | tdh     | 12          | 10    | -      | -     | -      | -     | ns      |

| Reset pulse width                               | tRES    | 1           | 0     | -      |       |        | -     | us      |

# Table 9.1-1 Pixel timing

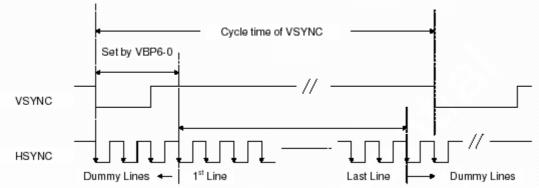

# a) Horizontal Data Transaction Timing

b) Vertical Data Transaction Timing

| Figure 9.1-2 Data                     | transaction | timina | (SYNC mode)                             |

|---------------------------------------|-------------|--------|-----------------------------------------|

| · · · · · · · · · · · · · · · · · · · |             |        | (•••••••••••••••••••••••••••••••••••••• |

| Characterist                 |           | Symbol         | Mi     | n     | Ту     | /p    | М      | ax    | Unit    |  |

|------------------------------|-----------|----------------|--------|-------|--------|-------|--------|-------|---------|--|

| Characterist                 | ics       | Symbol         | 24 bit | 8 bit | 24 bit | 8 bit | 24 bit | 8 bit | Unit    |  |

| DOTCLK Frequency             | у         | fDOTCLK        | -      | -     | 6.5    | 19.5  | 10     | 30    | MHz     |  |

| DOTCLK Period                |           | tDOTCLK        | 100    | 33.3  | 154    | 51.3  | -      | -     | ns      |  |

| Horizontal Frequen           | cy (Line) | fH             | -      |       | 14     | .9    | 22     | .35   | KHz     |  |

| Vertical Frequency (Refresh) |           | fV             | -      |       | 6      | 0     | ç      | 90    | Hz      |  |

| Horizontal Back Po           | rch       | tHBP           | -      | -     | 68     | 204   | -      | -     | tDOTCLK |  |

| Horizontal Front Po          | rch       | tHFP           | -      | -     | 20     | 60    | -      | -     | tDOTCLK |  |

| Horizontal Data Sta          | rt Point  | tHBP           | -      | -     | 68     | 204   | -      | -     | tDOTCLK |  |

| Horizontal Blanking          | Period    | tHBP +<br>tHFP | -      | -     | 88     | 264   | -      | -     | tDOTCLK |  |

| Horizontal Display A         | Area      | HDISP          | -      | -     | 320    | 960   | -      | -     | tDOTCLK |  |

| Horizontal Cycle             |           | Hcycle         | -      | -     | 408    | 1224  | 450    | 1350  | tDOTCLK |  |

| Vertical Back Porch          | 1         | tVBP           | -      |       | 18     |       | -      |       | Lines   |  |

| Vertical Front Porch         | ۱         | tVFP           | -      |       | 4      | 4     |        | -     | Lines   |  |

| Vertical Data Start I        | Point     | tVBP           | -      |       | 18     | 8     |        | -     | Lines   |  |

| Vertical Blanking Pe         | eriod     | tVBP +<br>tVFP | -      |       | 22     |       |        | -     | Lines   |  |

| Vortical Display             | NTSC      |                |        |       | 24     | 10    |        |       |         |  |

| Vertical Display<br>Area     | PAL       | VDISP          | -      |       | 280(PA | LM=0) |        | -     | Lines   |  |

| 71100                        |           |                |        |       | 288(PA | LM=1) |        |       |         |  |

| Vertical Cycle               | NTSC      | Vcycle         | -      |       | 26     | 62    | - 3    | Lines |         |  |

|                              | PAL       | veycle         |        |       | 31     | 3     | 5      | Lines |         |  |

| SEL[2:0]=100,   | NTSC/PAL Hcycle=1560                                                 |

|-----------------|----------------------------------------------------------------------|

| HSYNC           |                                                                      |

|                 |                                                                      |

| DOTCLK          |                                                                      |

| R[7:0]          | Invalid Data Cr1 Y1 Cb1 Y2 Cr320 Y639 Cb320 Y640 Invalid Data        |

|                 | <b>4− </b> [tHBP=HBP[6:0]*4+STP[1:0] <b>+</b>                        |

| SEL[2:0]=101,   |                                                                      |

|                 |                                                                      |

| HSYNC           |                                                                      |

| DOTCLK          |                                                                      |

| R[7:0]          | Invalid Data Cr1 X Y1 X Cb1 X Y2                                     |

|                 | <b></b>                                                              |

| SEL[2:0]=101    | PAL                                                                  |

|                 | Hcycle=1728                                                          |

| HSYNC           |                                                                      |

| DOTCLK          |                                                                      |

| R[7:0]          | Invalid Data Cr1 Y1 Cb1 Y2 Cb1 Y2 Cr360 Y719 Cb360 Y720 Invalid Data |

|                 | <b>■</b>                                                             |

| SEL[2:0]=110,   |                                                                      |

|                 | Hcycle=1716                                                          |

| HSYNC           |                                                                      |

| DOTCLK          |                                                                      |

| R[7:0]          | Invalid Data Cb1 Y1 Cr1 Y2                                           |

|                 | ≠− <b>t</b> HBP=HBP[6:0]*4+STP[1:0] → ≠ HDISP=1440 →                 |

| SEL[2:0]=110,   |                                                                      |

| HENDER          | ■ Hcycle=1728                                                        |

| HSYNC           |                                                                      |

| DOTCLK          |                                                                      |

| R[7:0]          | Invalid Data Cb1 X1 Cr1 X Y2                                         |

|                 | م-tHBP=HBP[6:0]*4+STP[1:0] -                                         |

| SEL[2:0]=111,   |                                                                      |

| l               | Hcycle=1560                                                          |

| TICSTAT         |                                                                      |

| HSYNC           |                                                                      |

| HSYNC<br>DOTCLK |                                                                      |

|                 | Invalid Data     Cb1 \ Y1 \ Cr1 \ Y2 \                               |

Figure 9.1-4 CCIR601 horizontal timing

| CTT 19.01 100 11 500   |                  |                                               |             | Conf                                | idential L | Document    |

|------------------------|------------------|-----------------------------------------------|-------------|-------------------------------------|------------|-------------|

| SEL[2:0]=100~11,NTSC   |                  |                                               |             |                                     |            |             |

| EVEN Fi                | eld 🗕 🗕          |                                               |             | ODD Field                           |            |             |

| vanic                  |                  |                                               |             |                                     |            |             |

| HSYNC                  | ШЩЦ              |                                               | $\Box$      |                                     |            |             |

| 1 2                    | 3 4 5 6          | 7                                             | 22          | 23 24 25                            | •••••      | 261 262     |

| R[7:0]                 | 4                |                                               | •           | DLI DL2 DL3                         | •••••      | DL239 DL240 |

|                        |                  |                                               | EVEN        | . Finla                             |            |             |

| VSYNC                  |                  |                                               |             |                                     |            |             |

|                        |                  |                                               |             |                                     |            |             |

| HSYNC 265 2            |                  |                                               | 285         |                                     |            | 524 525     |

| 207 205 2              | 10 207 208 207 2 |                                               |             |                                     |            | 324 323     |

| R[7:0]                 | 4                | — tvBP=vBP[6:0]+1                             |             | DLI DL2 DL3                         | •••••      | DL239 DL240 |

| SEL[2:0]=100~111,PAL,  | PALM=0           |                                               |             |                                     |            |             |

| – EVEN<br>Field        |                  |                                               | —ODD Field  |                                     |            |             |

| VSYNC                  | 1                |                                               |             | 1                                   |            |             |

|                        |                  |                                               |             |                                     |            |             |

|                        |                  | <u>,                                     </u> | 26          |                                     | ·····      | 305 306     |

|                        | 4                |                                               | _           |                                     |            | DL279 DL280 |

| R[7:0]                 | tvE              | P=VBP[6:0]                                    |             | DLI DL2 DL3                         |            | DL279 DL280 |

| ODD                    |                  |                                               |             | ld                                  |            |             |

| VSYNC                  |                  |                                               |             |                                     |            |             |

| HSYNC                  |                  |                                               |             | $i \square \square \square \square$ |            |             |

|                        |                  | 319                                           | 339         | 340 341 342                         |            | 618 619     |

| R[7:0]                 | - <b>f</b> rm    | P=VBP[6:0]+1                                  |             | DLI DL2 DL3                         |            | DL279 DL280 |

|                        |                  | r- 4Dr[0:0]+1                                 | _           |                                     |            |             |

| SEL[2:0]=100~111,PAL,F | ALM=1            |                                               |             |                                     |            |             |

| _EVEN<br>Field         |                  |                                               | -ODD Field  | I                                   |            |             |

| VSYNC                  |                  |                                               |             |                                     |            |             |

| HSYNC                  |                  |                                               |             | juuu                                |            |             |

| 1 2                    | 3 4 5 6          | 7                                             | 22          | 23 24 25                            |            | 309 310     |

| R[7:0]                 | tvb              | P=VBP[6:0]                                    |             | DLI DL2 DL3                         |            | DL287 DL288 |

| I                      |                  |                                               |             |                                     |            |             |

|                        |                  |                                               | —— EVEN Fie | 1d                                  |            |             |

| ODD<br>Field           |                  |                                               |             |                                     |            |             |

|                        |                  |                                               |             | imm                                 |            |             |

| Field                  |                  |                                               |             |                                     |            |             |

| Field Field            | 15 316 317 318 3 | <u>19</u>                                     | 335         | 336 337 338                         | ·····      | 622 623     |

Figure 9.1-5 CCIR601 vertical timing

|             | 1MAGE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Confidential Document                                                            |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| SEL[2:0]=01 | 10,NTS C/PAL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                  |

| DOTCLK      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                  |

| R [7:0]     | (FF X 00 X 00 XEAV X Invalid Data X FF X 00 X 00 X SAV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | (Ch1 / Y1 / Cr1 / Y2 ) (F320/Y639 ) (F320/Y640 / FF / 00 / 00 / EAV / Invalid Da |

|             | *                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ← HDISP=1280 →                                                                   |

|             | + Hcycle=150                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | i0                                                                               |

| SEL[2:0]=01 | 11,NTSC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                  |

|             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                  |

| R [7:0]     | FF         X 00         X EAV         Invalid Data         FF         X 00         X 00         X SAV           +         -         t HBP=HBP[6:0]*4.STP[1:0]         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -          - | (1) Y1 (1) (1) (1) (1) (1) (1) (1) (1) (1) (1                                    |

|             | + Hcycle=17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 16                                                                               |

| SEL[2:0]=0  | 11,PAL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                  |

| DOTCLK      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                  |

| R [7:0]     | (FF X00 X00 XEAV) Invalid Data X FF X00 X00 X SAV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | (Cb1 Y1 (Cr1 Y2)(Cb366(Y719)(Cr366)(Y720)(FF (0 0 (EAV / Invalid Da              |

|             | ← t HBP=HBP[6:0]*4-STP[1:0]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ← HDISP=1440 →                                                                   |

Hcycle=1728

# Figure 9.1-6 CCIR656 horizontal timing

| SEL[2:0] = 010, 011, NTSC (F=0 → ODD field, F=1 → EVEN field)                                                                                                                                                                                                      |                                 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| H L L L L L L L L L L L L L L L L L L L                                                                                                                                                                                                                            |                                 |

| V<br>F<br>R [7:0] [0239 [0239 [0230]                                                                                                                                                                                                                               | DL1 DL2 DL3 DL4                 |

| H 1. C.                                                                                                                                                                                                                        |                                 |

| V<br>F<br>R [7:0] [01.229 [01.249]                                                                                                                                                                                                                                 | DL1 DL2 DL3 DL4                 |

|                                                                                                                                                                                                                                                                    |                                 |

| $\begin{array}{c} \text{SEL}[2:0] = 010, 011, \text{PAL, PALM=0} (\text{F=0} \rightarrow \text{ODD field}, \text{F=1} \rightarrow \text{EVEN field}) \\ \\ \text{H} \\ \hline \\ $ |                                 |

| v                                                                                                                                                                                                                                                                  | DIA DI2 DI3 DI4                 |

| H 1_1_1_1_1_1_1_1_12_313_314_315                                                                                                                                                                                                                                   |                                 |

| F                                                                                                                                                                                                                                                                  |                                 |

| r<br>R [7:0]                                                                                                                                                                                                                                                       | ► DL1 DL2 DL3                   |

| $\text{SEL}[2:0] = 010, 011, \text{PAL}, \text{PALM}=1 \text{ (F}=0 \rightarrow \text{ODD field}, \text{F}=1 \rightarrow \text{EVEN field})$                                                                                                                       |                                 |

| H 1_1_1_1_1_1_1_1_1_1_1_1_1_1_1_1_1_1_1_                                                                                                                                                                                                                           |                                 |

|                                                                                                                                                                                                                                                                    |                                 |

| r<br>t <sub>VEP</sub> = VBP[6:0]                                                                                                                                                                                                                                   |                                 |

| R [7:0] [01285 [01286 [01286 [01286 ]01286 ]01287 [01288                                                                                                                                                                                                           | DL1 DL2 DL3 DL4 DL5 DL4 DL7 DL8 |

| H L L L L L L L L L L L L L L L L L L L                                                                                                                                                                                                                            |                                 |

| V<br>F<br>R[7:0] 01296 01296 01296 01297 01298 01297 01298                                                                                                                                                                                                         | DL1 D12 DL3 DL4 DL5 DL6 DL7     |

|                                                                                                                                                                                                                                                                    |                                 |

Figure 9.1-7 CCIR656 vertical timing

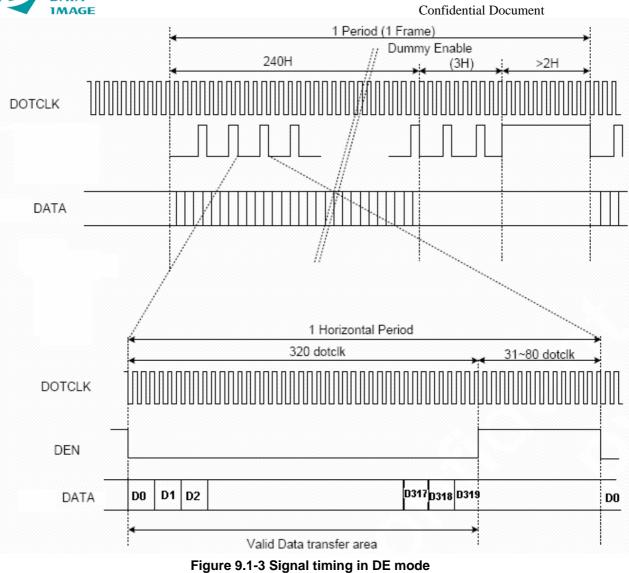

| Characteristics                                                                                     | Symbol               | Min | Тур | Max | Units |

|-----------------------------------------------------------------------------------------------------|----------------------|-----|-----|-----|-------|

| VCI / VDDIO on to falling edge of SHUT                                                              | tp-shut              | 1   | -   | -   | us    |

| DOTCLK to falling edge of SHUT                                                                      | tclk-shut<br>(Note1) | 1   | -   | -   | clk   |

| Falling edge of SHUT to display start<br>-1 line: 408 clk<br>-1 frame: 262 line<br>-DOTCLK = 6.5MHz | tshut-on<br>(Note1)  | -   | -   | 14  | frame |

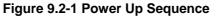

Note1 : It is necessary to input DOTCLK before the falling edge of SHUT.

Note 2: Display starts at 10th falling edge of VSYNC after the falling edge of SHUT.

The display starts at the falling edge to VSYNC which is determined by BLT[1:0] of R04h.

# Table 9.2-1 Power Up Sequence

| -                            |              |                |                            |                    |                   |            |                | <b>`</b>    |

|------------------------------|--------------|----------------|----------------------------|--------------------|-------------------|------------|----------------|-------------|

| VDDIO                        |              |                |                            |                    |                   |            |                | \           |

| Vсı                          |              |                |                            |                    |                   |            |                |             |

| RESET                        |              |                |                            |                    |                   |            |                |             |

| SPI                          |              |                | SPI accessing              |                    |                   |            |                |             |

| SHUT                         | /            | /              |                            |                    |                   |            |                |             |

| DOTCLK                       |              |                |                            |                    |                   |            |                |             |

| HSYNC                        |              |                |                            |                    |                   |            |                |             |

| VSYNC                        |              |                | st 2nd                     | 3rd                | 4th               | 5th 6      | th             |             |

| VCIX2                        |              |                |                            |                    |                   |            | loating        | *****       |

| VLCD6                        | 3            |                |                            |                    |                   |            | <br>loating    |             |

| VCIM                         |              |                |                            |                    |                   | F          | loating        | · · · · · · |

| VGH                          |              |                |                            |                    |                   | Flo        | pating         |             |

| VGL                          |              |                |                            |                    |                   |            | /GLdischarge t | to ground   |

| Gate/POI                     | ./PWM( If PW | <br>M turn-on) |                            |                    |                   |            |                |             |

| SOUT<br>(S0~S959)            | Normal Displ | ау             | lack Pattern (for normally | Black), or White I | Pattern (for noma | lly White) |                |             |

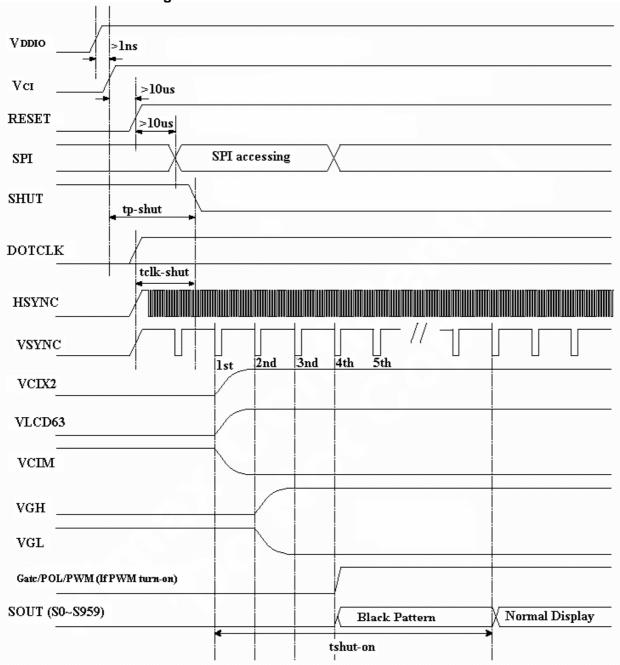

| •                            |              | 4              |                            | tshut-off          |                   |            |                |             |

|                              |              | Fig            | gure 9.2-2 Powe            | er Down Se         | quence            |            |                |             |

|                              | racteristics |                | Symbol                     | Min                | Тур               | Max        | Unit           |             |

|                              | SHUT to disp | play off       |                            |                    |                   |            |                |             |

| ine: 408 clk<br>rame: 262 li | ne           |                | Tshut-off                  | -                  | -                 | 6          | frame          |             |

Note: DOTCLK must be maintained at lease 6 frames after the rising edge of SHUT. Display become off at the 6th falling edge of VSYNC after the falling edge of SHUT. If RESET signal is necessary for power down, provide it after the 6-frames-cycle of the SHUT period. Table 9.2-2 Power Down Sequence

-DOTCLK = 6.5MHz

#### 9.3 Serial Interface

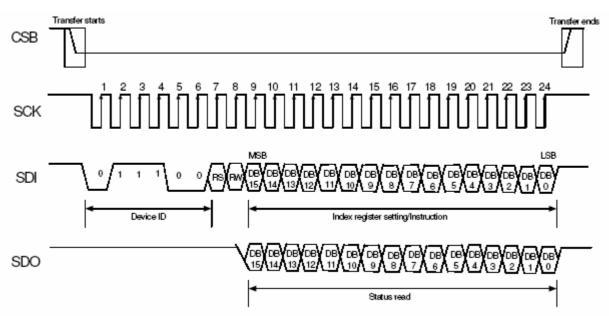

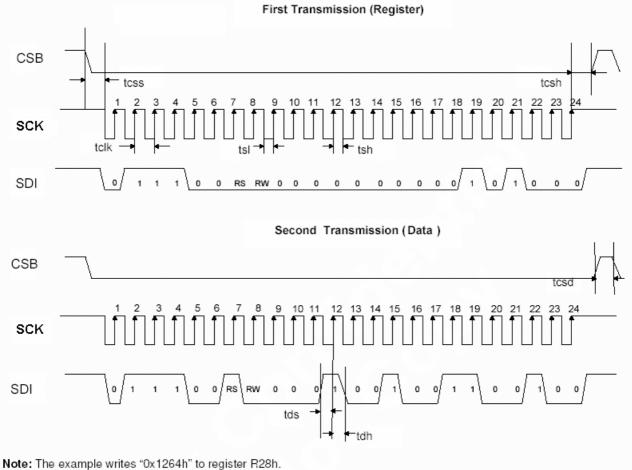

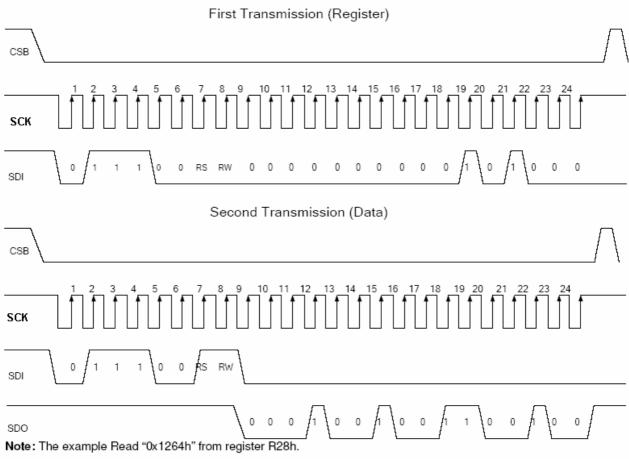

The SPI is available through the chip select line (CSB), serial transfer clock line (SCK), serial data input (SDI), and serial data output (SDO).

The Driver IC recognizes the start of data transfer at the falling edge of CSB input to initiate the transfer of start byte. It recognizes the end of data transfer at the rising edge of CSB input. The Driver IC is selected when the 6-bit chip address in the start byte transferred from the transmission device and the 6-bit device identification code assigned to the Driver IC are compared and both 6-bit data correspond. The identification code must be 011100. Two different chip addresses must be assigned to the Driver IC because the seventh bit of the start byte is assigned to a register select bit (RS). When RS = 0, index register write or status read is executed. When the RS = 1, instruction write. The eighth bit of the start byte is to specify read or write (R/W bit). The data are received when the R/W bit is 0, and are transmitted when the R/W bit is 1.

After receiving the start byte, the Driver IC starts to transmit or receive data by byte. The data transmission adopts a format by which the MSB is first transmitted (9th SCK started). All Driver IC instructions consist of 16 bits and they are executed internally after two bytes are transmitted with the MSB first (IB15 to 0---9th ~24th SCK).

| RS                 | RW                | status                  |  |  |  |  |  |  |  |  |

|--------------------|-------------------|-------------------------|--|--|--|--|--|--|--|--|

| 0                  | 0                 | Write SPI address       |  |  |  |  |  |  |  |  |

| 1 0 Write SPI data |                   |                         |  |  |  |  |  |  |  |  |

| 1                  | 1 1 Read SPI data |                         |  |  |  |  |  |  |  |  |

|                    | Та                | ble9.3-1RS & RW setting |  |  |  |  |  |  |  |  |

# Figure9.3-1 SPI Timing

Under the standard condition, the number of CLK is twenty-four units. After CSB has transmitted twenty-four units of CLK, it has to change into High. When the number of CLK is less than 24 units, the data of SPI can't be downloaded. When the number of CLK is more than 25 units, the data of SPI will download the former data of the 24 units of CLK.

Iote: The example writes "0x1264h" to register R28 SPID connected to VSS.

# Figure 9.3-2 SPI interface Timing Diagram & W rite SPI Example

# Figure 9.3-3 SPI interface Timing Diagram & Read SPI Example

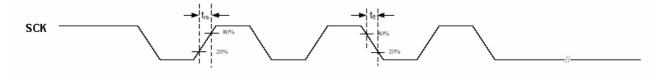

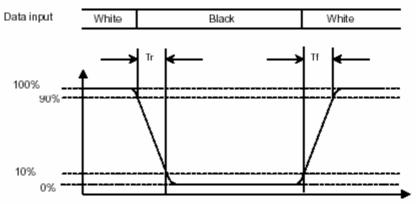

# Figure9.3-4Rising/Falling time

| Characteristics             | Symbol | Min. | Тур. | Max. | Unit |

|-----------------------------|--------|------|------|------|------|

| Serial Clock Frequency      | fclk   | -    | -    | 20   | MHz  |

| Serial Clock Cycle Time     | tclk   | 50   | -    | -    | ns   |

| Clock Low Width             | tsl    | 25   | -    | -    | ns   |

| Clock High Width            | tsh    | 25   | -    | -    | ns   |

| Clock Rising Time           | trs    | -    | -    | 30   | ns   |

| Clock Falling Time          | tfl    | -    | -    | 30   | ns   |

| Chip Select Setup Time      | tcss   | 0    | -    | -    | ns   |

| Chip Select Hold Time       | tcsh   | 10   | -    | -    | ns   |

| Chip Select High Delay Time | tcsd   | 20   | -    | -    | ns   |

| Data Setup Time             | tds    | 5    | -    | -    | ns   |

| Data Hold Time              | tdh    | 10   | -    | -    | ns   |

# Table 9.3-2 SPI timing

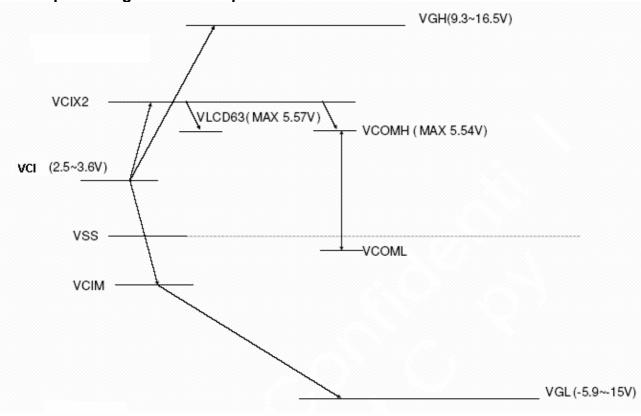

Figure 9.4-1 LCD driving voltage relationship Note: The above voltages level assumed 100% efficiency of the internal booster. There has no voltage drop due to resistance from ITO trace of the panel.

#### **10.1 Command Table**

| Resolute                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | -    |             |     |          |       |       |       |       |       |       |       |       |       |      |      |      |      |      |      |      |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------------|-----|----------|-------|-------|-------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|------|

| SR         Read         To         O         To         D         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O         O        O        O         O <th>Reg#</th> <th></th> <th>R/W</th> <th>R/S</th> <th>IB15</th> <th>IB14</th> <th>IB13</th> <th>IB12</th> <th>IB11</th> <th>IB10</th> <th>IB9</th> <th>IB8</th> <th>IB7</th> <th>IB6</th> <th>IB5</th> <th>IB4</th> <th>IB3</th> <th>IB2</th> <th>IB1</th> <th>IB0</th>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Reg# |             | R/W | R/S      | IB15  | IB14  | IB13  | IB12  | IB11  | IB10  | IB9   | IB8   | IB7   | IB6  | IB5  | IB4  | IB3  | IB2  | IB1  | IB0  |

| R0h         conduit         con                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | SR   | Read        | 1   | 0        | L7    | L6    | L5    | L4    | L3    | L2    | L1    | L0    | 0     | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

| control         0         1         0         R         K         V         B         C         C         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0        0         0         0 <td>R01h</td> <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | R01h |             |     |          |       |       |       |       |       |       |       |       |       |      |      |      |      |      |      |      |

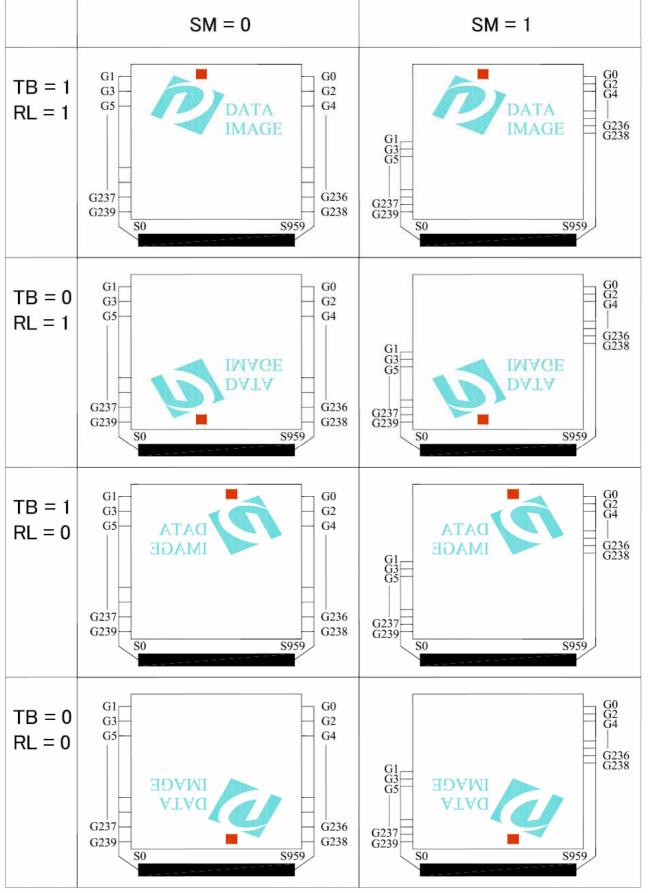

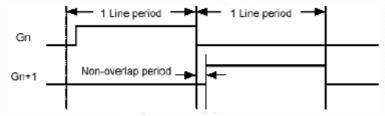

| R2D2         chiver AC         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0        0        0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |      | control     | 0   | 1        | 0     | RL    | REV   | PINV  | BGR   | SM    | TB    | CPE   | 0     | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

| R3B         Convert         0         1         DC13         DC71         DC10         BTF         BT0         BT0         DC3         DC2         DC1         DC0         AP1         AP1<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | R02h |             |     |          |       |       |       |       |       |       |       |       |       |      |      |      |      |      |      |      |

| Nome         Control (1)         O         I         Data of 10         Data of 10 <thdat< td=""><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td>-</td><td></td><td></td></thdat<>                                                                                                                                                                                                                                                     |      |             |     |          |       |       |       |       |       |       |       |       |       |      |      |      |      | -    |      |      |

| RNM         Color lifer         0         1         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0        0 <t< td=""><td>R03h</td><td>control (1)</td><td>0</td><td>1</td><td>DCT3</td><td>DCT2</td><td>DCT1</td><td>DCT0</td><td>BTF</td><td>BT2</td><td>BT1</td><td>BT0</td><td>DC3</td><td>DC2</td><td>DC1</td><td>DC0</td><td>AP2</td><td>AP1</td><td>AP0</td><td>0</td></t<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | R03h | control (1) | 0   | 1        | DCT3  | DCT2  | DCT1  | DCT0  | BTF   | BT2   | BT1   | BT0   | DC3   | DC2  | DC1  | DC0  | AP2  | AP1  | AP0  | 0    |